FPGA Design

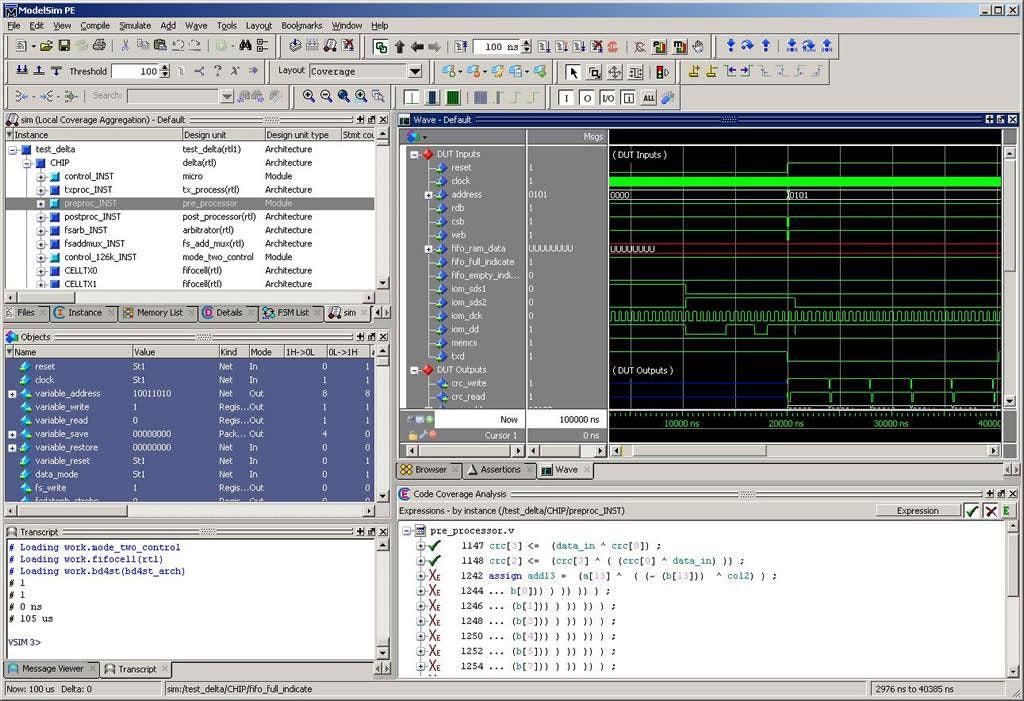

Integrated FPGA Design Flow

Ferramentas para desenvolvimento de lógica programável independente do fabricantes de FPGA (integra com as ferramentas de place e route dos fabricantes).

Seja para projetar um FPGA ou um ASIC, os dispositivos têm recursos avançados e recursos complexos que, quando submetidos a ciclos de desenvolvimento restritos, sobrecarregam as equipes de projeto cujo objetivo é produzir chips eficientes e robustos. Portanto, as equipes de design impuseram mais demandas aos processos de HDL, automação e diretrizes de estilo para o desenvolvimento de resultados de qualidade.

Linguagens padrão (como VHDL, Verilog, SystemVerilog) e formatos IP, juntamente com sistemas de gerenciamento de versões comuns do setor, ajudam a produzir processos de design repetíveis e confiáveis, mas as ferramentas que utilizam esses padrões precisam fazer muito mais do que editar arquivos de texto.

A Mentor Graphics oferece uma solução de design completa para o desenvolvimento de FPGA e ASIC HDL, começando com a criação abrangente do design, abordando a criação de novos códigos, a reutilização formal e informal do design e qualquer combinação entre eles. Esses recursos de design HDL auxiliam bastante os engenheiros, indivíduos e equipes na criação, análise e gerenciamento de projetos complexos, melhorando sua produtividade e acelerando a criação do projeto.